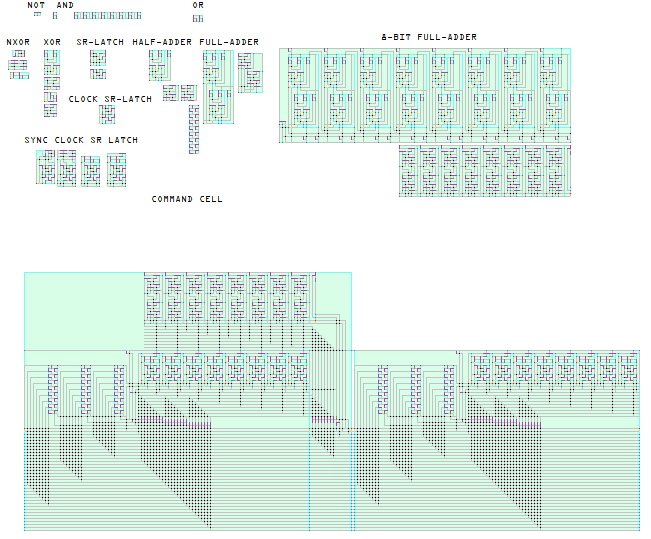

8-Bit Computer with Novel Integrated Memory Architecture

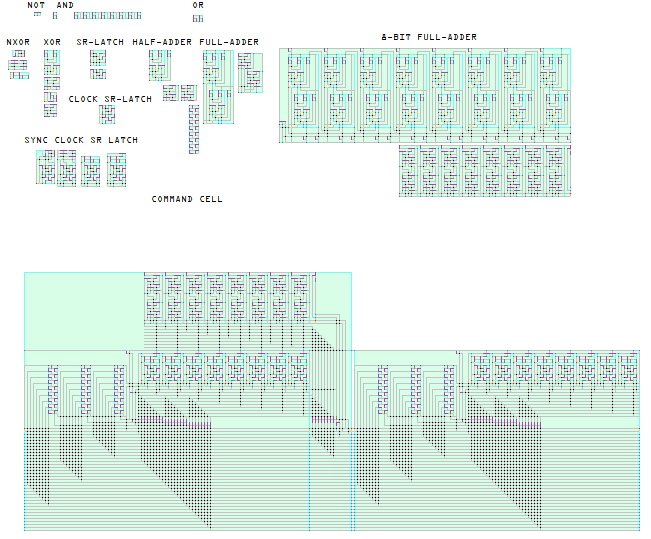

I’ve designed an 8-bit computer uses memory similar to x86 systems but instructions are assigned to cells which proceed to manipulate the data on reception of it. This integrates processing as a function of memory. It uses only one hard instruction that corresponds to x86 mov. The Pilot cell (PLT) acts as the x86’s equivalent instruction pointer and up to 255 (max) cells can be added to the computer.

- The Next (NXT) flag is set which activates an ADD sequence in PLT.

- The Pilot cell (PLT) points to the Target (TGT) cell via the Pointer (PNT) bus.

- The TGT is comprised of Target Alpha (TGA, the memory cell activated) and Target Beta (TGB, the consecutive memory cell).

- TGA points to a Receiving cell (RCV), and TGB points to a Sender cell (SND).

- The Data bus (DAT) is used to copy from SND to RCV.

- On completion, the NXT flag is set and (1) continues.

goto instructions can be carried out by setting the PLT cell to the next instruction (minus 1). The advantage of this architecture is that the computer can be extended arbitrarily and hardware implemented functions can be added as memory cells.